### **Agilent Technologies**

## Wireless LAN – A Unified Physical Layer Design and Measurement Environment

March 6, 2002 presented by:

Speaker #1 Joe Troychak Speaker #2 Afshin Amini

Simulating and testing modern wireless radio systems requires accurate generation of complex modulated RF signals. Examples include third-generation (3G) cellular and wireless networking applications such as Bluetooth and wireless local area networking (WLAN). Simulation can help validate prototype IC designs early, resulting in shorter design cycles and faster production times. Obtaining good correlation between simulated and measured data provides for a closed loop design cycle. Moving complex signals, data, and test vectors between simulation and measurement domains further shortens the design cycle.

Simulating and testing a WLAN 802.11a receiver requires transmit packet bit-level accuracy of short and long preambles, signaling, and data contents. This transmit packet information is used for receiver phase, frequency, and timing adjustments. It is necessary for the receiver to operate in severe multi-path environments, and advantageous to perform simulations and measurements including multi-path distortion. Power amplifiers for 802.11a must meet linearity requirements for signals with peak-to-averages in excess of 10 dB. Simulating and testing with exactly the same complex modulated signals helps ensure that amplifier results correlate.

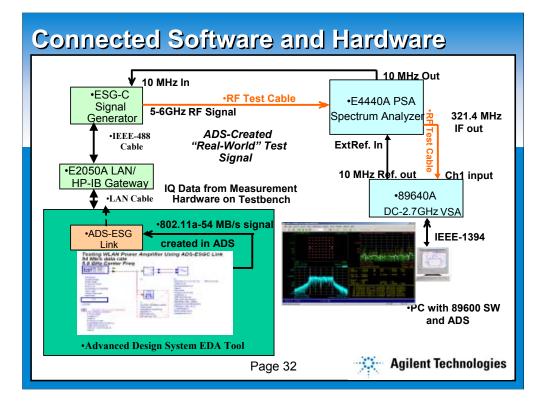

This paper will highlight virtual measurements within ADS simulations, and demonstrate hardware emulation using GPIB hardware links to an Agilent ESG IQ arbitrary waveform generator. Arbitrary IQ signals can originate in either the simulation or measurement domains, and captured for reuse within system level design, integration, and test. Results are recorded with an Agilent Vector Signal Analyzer (VSA) for reuse in simulations for evaluating hardware prototype designs and post-processing measured data.

### **Design Challenges of OFDM Modulation**

Page 4

Agilent Technologies

#### 1,2)Effect:

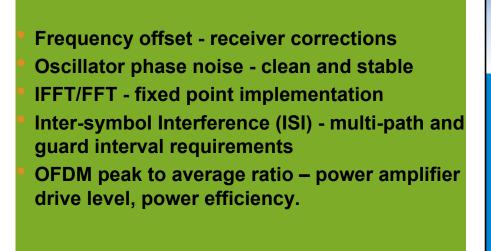

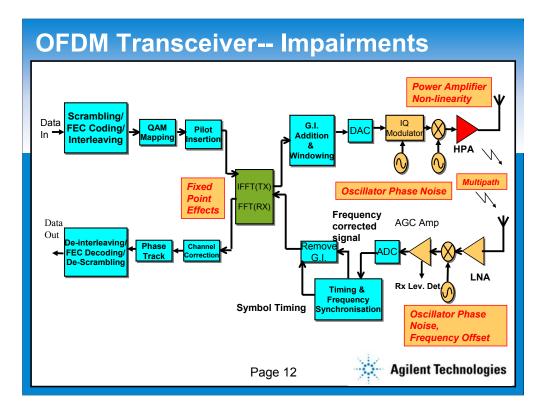

Frequency offset and phase noise both produce Inter-Carrier Interference (ICI). This ICI degrades the ability of the receiver (FFT) to distinguish between sub-carriers, i.e. Orthoginality is destroyed.

Likely Cause: oscillator

SO Designer need to be able to simulate and analyze the impact of oscillator and circuit designer need to know the boundary of design parameters. The engineer working on the Receiver needs to be fully aware of frequency synchronization and phase tracking algorithms and impact of RF front end and how to work them together

#### 3)Effect:

Fixed point processing produces uncertainty due to the quantization effects imposed on the modulated symbols as signal get processed thought the IFFT and FFT.

Likely Cause: poor choice of digital HW

SO Designer need to be able to choose the HW that gives him best tradeoff between power/size visavis signal fidelity.

4) Effect:

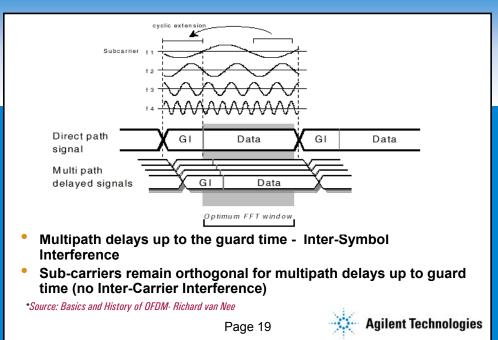

Multipath causes ISI- it is mitigated with extending each subcarrier beyond the symbol time called Guard Interval:IEEE802.11a has a 800 nsec GI

Likely cause: outdoor channel-mobility

SO designer Beyond 800 nsec need to have an environment to quickly analyze the signal degradation caused by multipath

5) Effect

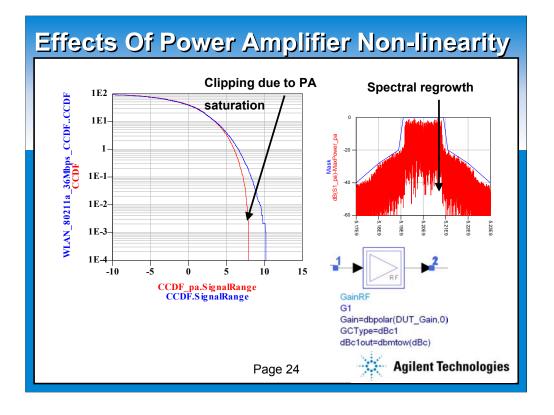

PA Operating in the non-linear region ca uses signal degradation- back off causes inefficiency in power

Likely cause: no cause- NEED a great PA design! That works in your system

SO PA and system designer designers need an integrated environment to be able to design and simulate and verify their circuit and test the HW in a consistent way

#### NEED:

#### **INTEGRATED DESIGN ENVIRONMENT**

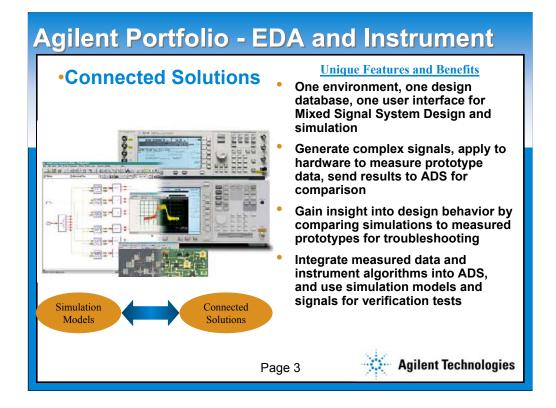

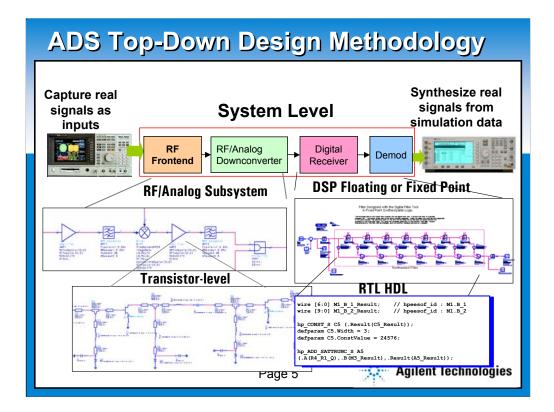

Once design requirements flow down from SYSTEM to RF and DSP designers, they can begin working on detailed circuit and DSP designs. The top level system design can then be used as a template for evaluating the effects of a circuit or DSP design on the overall system performance for bottoms-up verification.

For example, let's say that you are designing a 5 GHz PA to be used in a 802.11a transmitter which has a certain modulation accuracy specification. This is not an intuitive specification for the PA designer... However, the detailed PA circuit design, could be inserted back into the top level design to evaluate how the PA performance impacts the overall modulation accuracy performance.

This ability to mix levels of abstraction, using detailed RF circuit and DSP designs, when available, and functional elements when detailed designs aren't available, allows the overall system performance to be evaluated at every stage in the design process to reduce risk.

ADS's link to test instrumentation provides a final level of abstraction, where the measured performance of a hardware prototype can be inserted back into the top level system to evaluate it's effect on the overall system performance.

## IEEE802.11 PHY Layer

| SYSTEM     | FREQUENCY<br>BAND | MAX<br>DATA         | TRANSMIT<br>SCHEME |        |      | MODULATION |       |       |       |

|------------|-------------------|---------------------|--------------------|--------|------|------------|-------|-------|-------|

|            |                   | RATES<br>(MBPS)     | CCK                | PBCC   | OFDM | BPSK       | QPSK  | 16QAM | 64QAM |

| 802.11b    | 2.4GHz            | 11                  |                    | Option |      | Diff.      | Diff. |       |       |

| 802.11g    | 2.4GHz            | 54                  |                    | Option |      | Diff.      | Diff. |       |       |

| 802.11a,h  | 5GHz              | 36, option<br>to 54 |                    |        |      |            |       |       |       |

| HiperLAN/2 | 5GHz              | 54                  |                    |        |      |            |       |       |       |

| HiSWAN     | 5GHz              | 54                  |                    |        |      |            |       |       |       |

Page 6

Agilent Technologies

Emerging markets- low mobility wireless

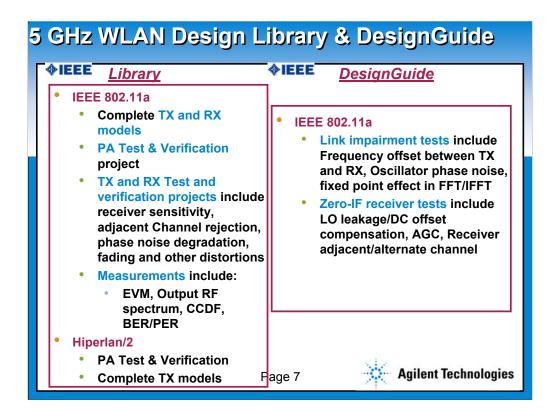

Agilent E8874A 5 GHz WLAN Design Library

The 5 GHz WLAN Design Library from Agilent EEsof EDA lets designers successfully develop high data rate Wireless LAN communications products based on the IEEE802.11a and Hiperlan2 standards. With this library, designers develop and refine specification-compliant algorithms at the system level, where design choices have the greatest impact, and quickly move designs to implementation.

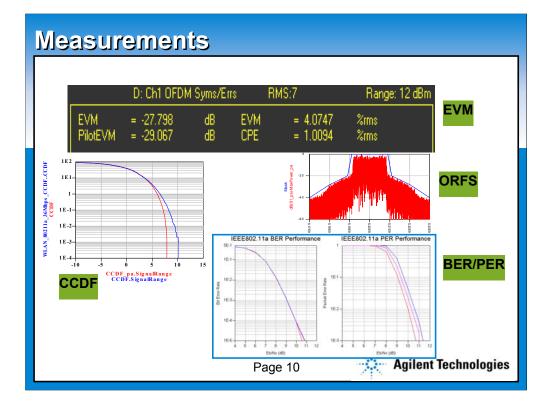

The 5 GHz WLAN Design Library is designed for use with Agilent's Advanced Design System 2001(ADS 2001), the powerful EDA design and simulation software package for communication system, RF and microwave designers of all types. The library includes pre-configured test and verification setups for evaluating designs and testing performance parameters such as Output RF Spectrum, Error Vector Magnitude (EVM), Power Statistics using Complementary Cumulative Distribution Function (CCDF), and Bit Error Rate/ Packet Error Rate (BER/PER) for the IEEE802.11a standard. Hiperlan2 transmitter models and test and verification setups help designers evaluate Output RF Spectrum, ACPR, and Power Statistics using the Complementary Cumulative Distribution Function (CCDF).

For more information about the 5 GHz WLAN Design Library or ADS 2001, visit www.agilent.com/eesof-eda.

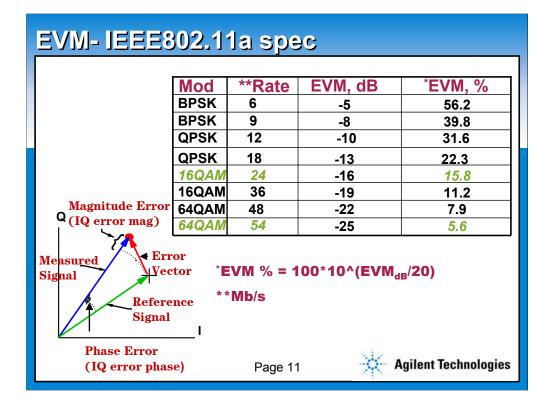

"Error Vector Magnitude" (EVM) as a measure of modulation quality. This metric has become an industry standard for a wide variety of applications from cellular to cable television. The basic idea behind EVM is that any impaired signal (usually complex signals) can be represented as the sum of an ideal signal and an error signal. Since the error signal can't be measured directly, the test instrumentation determines the error signal by reconstructing the ideal signal based on the detected data and subtracting it from the actual signal.

The error signal includes all sources of error including:

- Additive Noise

- Nonlinear distortion

- Linear Distortion (equalized in 802.11A)

- Phase Noise

- Spurious

- Other Modulation errors

Table shows the IEEE802.11a standard modulation quality in terms of EVM

In the table we have highlighted the percentage EVM at rates of 24Mb/s which uses 16QAM for sub-carrier modulations and 54 Mb/s that uses 64QAM- it can be seen from table at higher data rates the EVM becomes smaller as a result of tighter constellation points.

We saw the EVM numbers in the previous slides-

Now let's take a look at a transceiver path and correlate the impairment with the the likely cause.

#### NEEDMODELS THAT SATISFY EVOLVING SPECS

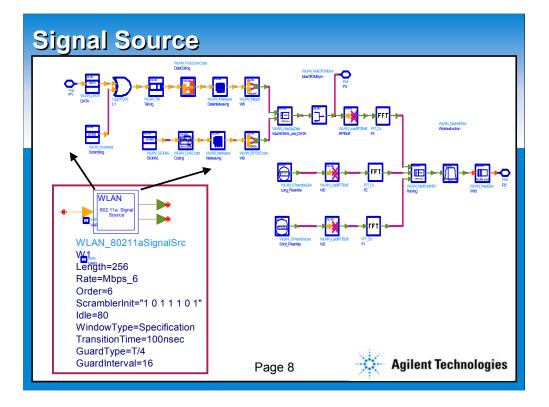

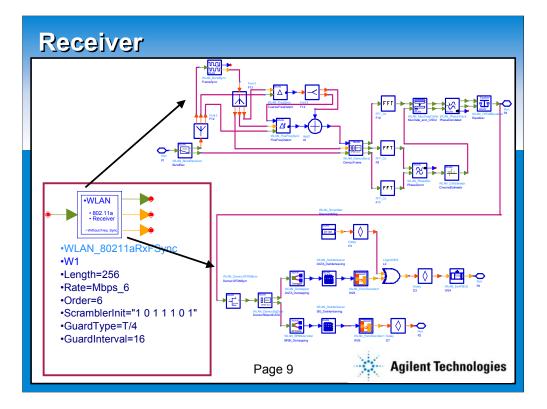

We talked about the 5 main design challenges of OFDM.

We need set of models that we could easily use to create coded signals at various data rates of IEEE802.11a, namely: 6-54 Mb/s and beyond

We also need set of models to detect and demodulate each of these signals and finally gives BER and PER(Packet Error rate)

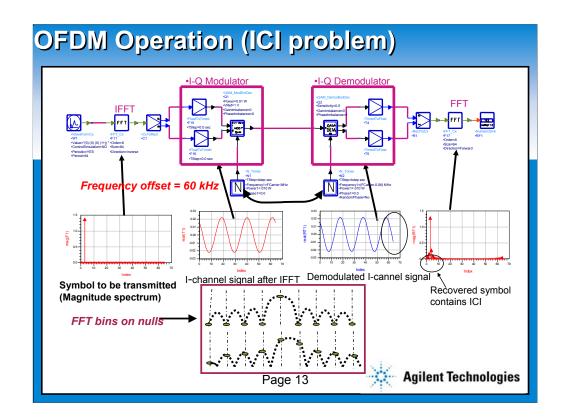

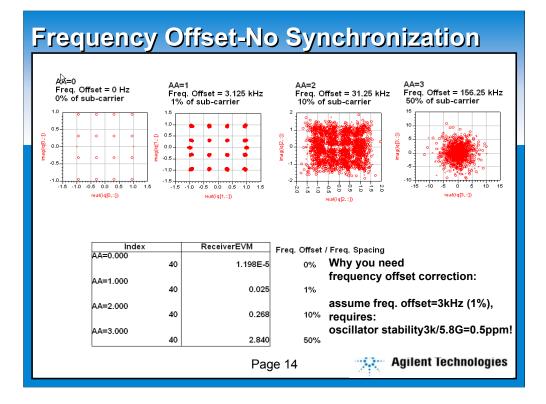

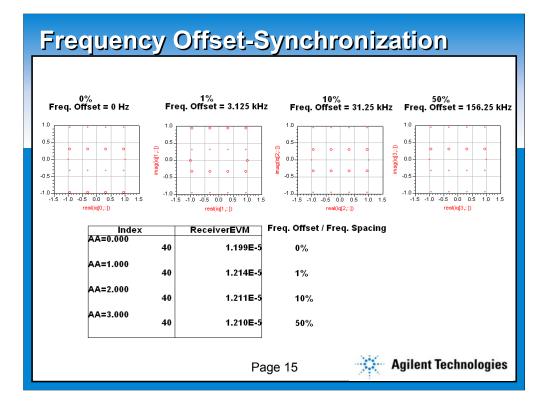

Frequency offset skews the sub-carrier in frequency which causes spectral leakage in the receiver's FFT. This leakage forces energy from one sub-carrier to fall inside the FFT bin of adjacent sub-carrier bins. This is what produces ICI.

This diagram shows how critical receiver frequency tracking is. If the receiver is off frequency, then the nulls in each carrier won't land on an FFT bin. In FFT terminology this is called leakage. For OFDM, the result is inter-carrier interference.

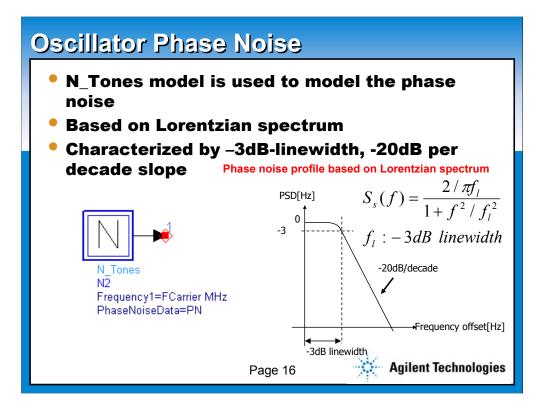

The power spectrum density of an oscillator signal with phase noise is modeled by a Lorentzian spectrum- it shows a squared magnitude of a first order LPF function.

Reference: R. van Nee et al. OFDM For Wireless Multimedia Communications Artech House 2000

Random phase variation:

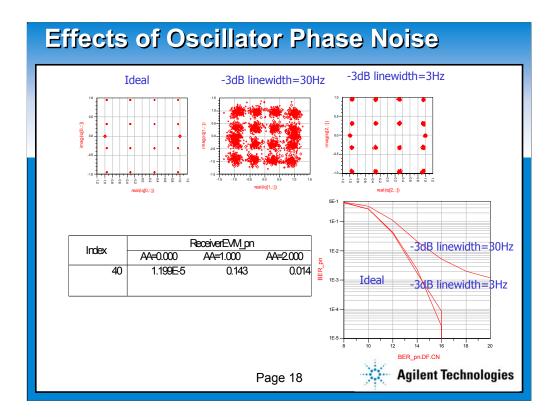

Phase tracking in the receiver can remove phase noise at very low frequencies that basically looks like a uniform shift in phase across all sub-carriers. This is accomplished during every OFDM symbol by monitoring the pilot signals.

In any ideal receiver phase tracking will track this out-i.e.. VSA software Phase Tracking option

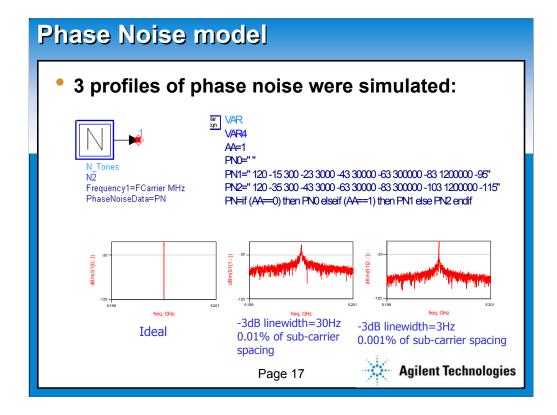

The more disturbing problem is ICI- studies show that with a phase noise profile as shown the 3 dB phase noise BW should be at the order of 0.01% of the sub-carrier spacing i.e.. 30 Hz for 312 KHz

Phase lock effects are not presented but can be simulated using the circuit representation and co-simulation power of ADS

This model for a local oscillator is a piece-wise construction of SSB phase noise. The noise will be created as a DSB spectrum within the analysis BW specified by the Tstep in the simulation. The spectrums shown are normalized to indicate the -3 dB bandwidth associated with integrating the phase noise power and comparing to the carrier power.

You can see that the ICI due to phase noise get worse as the phase noise spectrum BW (linewidth) becomes a larger percentage of the sub-carrier spacing.

Remember at lower phase noise SSB frequencies, the phase tracking capability of the OFDM receiver will correct the phase disturbance.

### **Guard Interval**

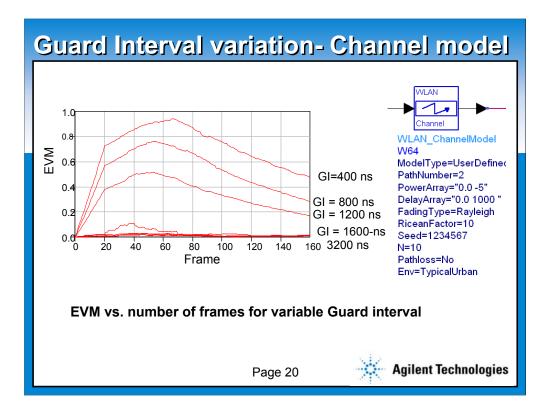

it's for non-802.11a applications, since GI is fixed in standard. But if range extension is needed, GI increases, and those apps require flexible GI and simulation is important.

This is the test at 48 Mb/s

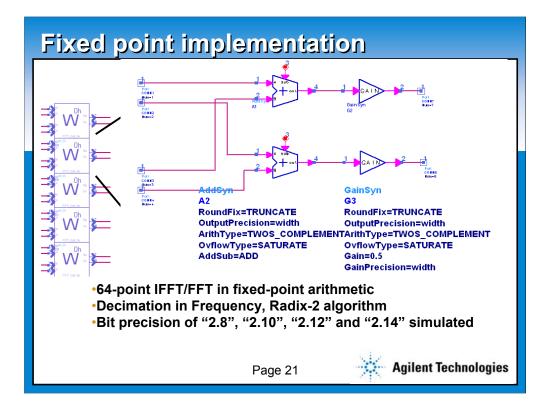

This is where you get one step closer to HW. At the level of fixed point blocks.

This is where you can create HDL code as well.

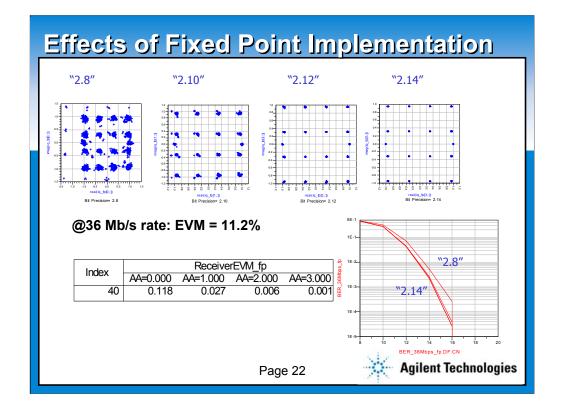

The simulation results show that as the wordlength of IFFT and FFT is reduced, the uncertainty associated with quantizing a QAM symbol will degrade the receiver performance. This is shown as both a degradation in EVM as well as a degradation in BER.

**Reference:**

Impact of front end non-idealities on Bit Error Rate Performances of WLAN-OFDM transceivers- B. Come, R Ness et al

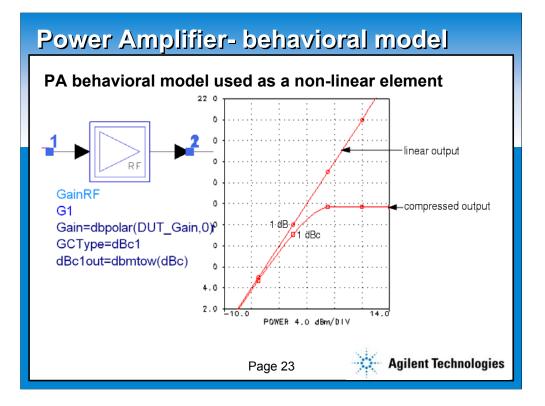

We show that gain\_RF behavioral model at the system level characterizes PA non-linearity by way of 1 dB compression point or level of back off.

-Before we treat the PA design and testing more rigorously

next we will revisit the instruments and the role they play early on in the design cycle for measurement and analysis of key parameters with in ADS environment

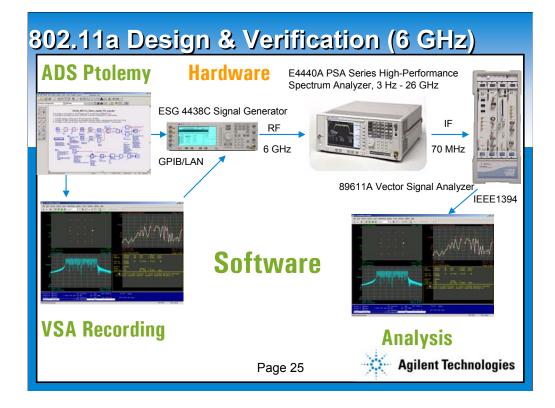

ADS 802.11a 16QAM modulation, 36 Mbps signal is simulated and analyzed with VSA software. Using ADS ESG-C links or the VSA hardware ESG-C links, download I and Q to the ESG dual-arbitrary waveform generator. The ESG hardware's 802.11a 6 GHz RF signal is analyzed by PSA/VSA. This allows ADS to emulate transmitter hardware. Radio impairments may include ISI, ICI, Phase Noise, PA nonlinearity, Multipath Delay Spread, or Power vs. Time.

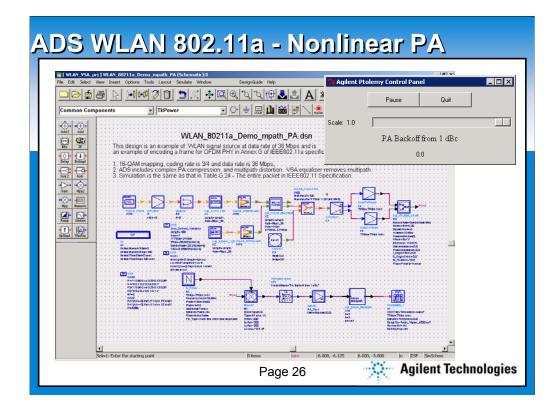

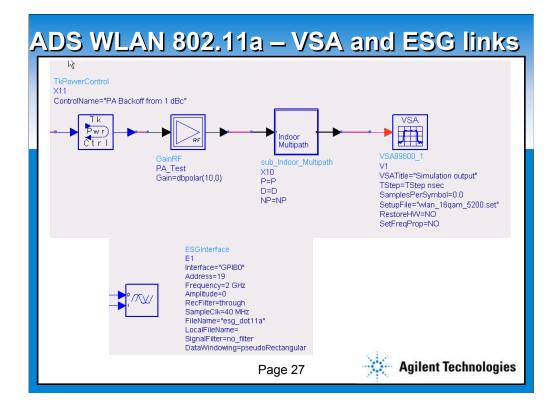

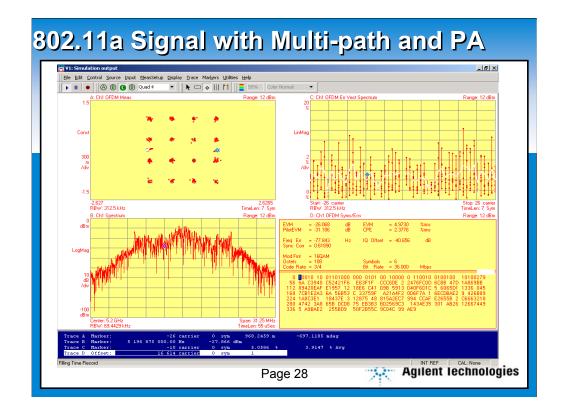

ADS simulation includes complex PA compression (large-signal S21 amplitude and phase in compression) and multipath distortion. Note effect of linear multipath distortion on spectrum, which is removed by VSA equalizer.

An interactive slider controls PA back off from 1-dB compression point. Adjust PA drive level real-time to meet the required 802.11a EVM specifications. Nonlinear effects are not removed by equalizer.

ADS simulation includes complex PA compression (large-signal S21 amplitude and phase in compression) and multipath distortion. Note effect of linear multipath distortion on spectrum, which is removed by VSA equalizer.

An interactive slider controls PA back off from 1-dB compression point. Adjust PA drive level real-time to meet the required 802.11a EVM specifications. Nonlinear effects are not removed by equalizer.

ADS simulation with VSA link display for software only analysis. Note multi-path effects on spectrum, which are removed by VSA equalizer.

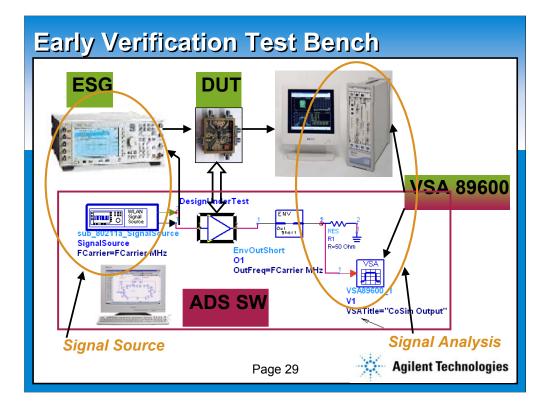

### Let's revisit ADS Design and Verification environment

Possibilities for this "Early Verification Test Bench"

include:

.Use simulation models or simulated circuit designs to fill-in for missing HW so verification testing can start earlier.

•Replace simulation models/circuits with hardware as fabrication progresses...verifying end-to-end performance of system at every stage

• Transition To & From design and test environment continuously to identify and fix issues early- where changes are easier/less costly to make

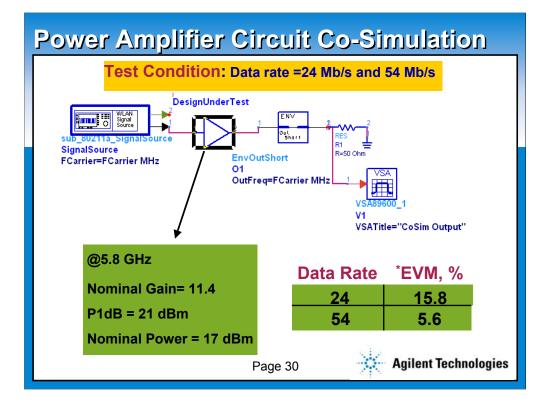

here is an early sample of a Power Amp tuned at 5.8 GHz. From the Preliminary data - here are some of its characteristics:

Nominal Gain = 11.4

(1 dB compression point) = 21 dBm

Nominal power == 17 dBm

What we need to know is that given the circuit model how far can we drive the PA before the value of EVM(Error Vector Magnitude) breaks down- Two modes are tested:

1-24 Mb/s which needs to meet 15.8% EVM

2- 54 Mb/s needs to meet 5.6% EVM

So we need to sweep the input power and measure the corresponding EVM. Since the gain is 11.4 we elected not to exceed 6 dBm input power-

Notice that the PA circuit model is being simulated with Circuit Envelop and the signal source with Ptolemy data flow simulation and measurement is handled by VSA software simulation- simultaneously in ADS environment

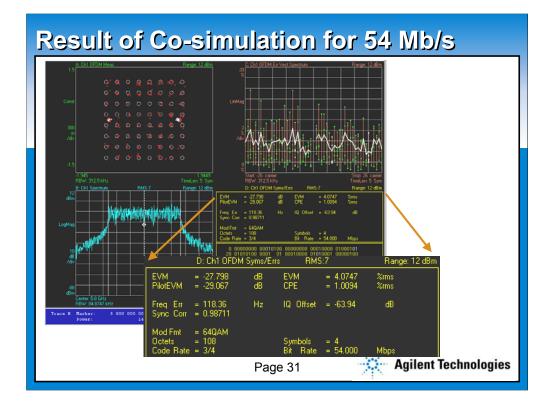

This shows 4.08% EVM

# Summary of results @ 24 Mbps, 5.8 GHz

| Condition                                  | EVM, dB          | EVM, %  | Comment            |

|--------------------------------------------|------------------|---------|--------------------|

| ADS/VSA, Pin =<br>+5 dBm                   | -20.9            | 9.0     | Pout=16.04<br>dBm  |

| ADS/VSA, Pin =<br>+6 dBm                   | -18.1            | 12.4    | Pout=16.84<br>dBm  |

| ADS/ESG-<br>C/DUT/VSA #64,<br>Pin = +5 dBm | -20              | 9.7     |                    |

| ADS/ESG-<br>C/DUT/VSA #64,<br>Pin = +6 dBm | -18.2            | 12.6    |                    |

| The specificati                            | on EVM is 15.8 % |         | ·                  |

|                                            | F                | Page 33 | Agilent Technologi |

| S | ummary o                                   | of results      | @54 Mb/ | s, 5.8 GHz        | 2 |  |  |

|---|--------------------------------------------|-----------------|---------|-------------------|---|--|--|

|   | Condition                                  | EVM, dB         | EVM, %  | Comment           |   |  |  |

|   | ADS/VSA, Pin =<br>+3 dBm                   | -27.8           | 4.08    | Pout=14.41<br>dBm |   |  |  |

|   | ADS/VSA, Pin =<br>+4 dBm                   | -24.5           | 5.9     | Pout=15.14<br>dBm |   |  |  |

|   | ADS/ESG-<br>C/DUT/VSA #64,<br>Pin = +3 dBm | -25.1           | 4.8     |                   |   |  |  |

|   | ADS/ESG-<br>C/DUT/VSA #64,<br>Pin = +4 dBm | -23.1           | 6.8     |                   |   |  |  |

|   | The specificatio                           | n EVM is 5.6 %. |         |                   | - |  |  |

|   | Page 34 Agilent Technologies               |                 |         |                   |   |  |  |

> The ability to mix levels of abstraction, using detailed RF circuit and DSP designs, when available, and functional elements when detailed designs aren't available, allows the overall system performance to be evaluated at every stage in the design process to reduce risk.

> Performance measures are dictated by 802.11a standard includes:

-EVM

-RF spectrum

-PER and BER

>Design Guide enable designer to check them against impairments and degradations caused by non-ideal circuits and components of real world.

>Use simulation models or simulated circuit designs to fill-in for missing HW so verification testing can start earlier. Replace simulation models/circuits with hardware as fabrication progresses...verifying end-to-end performance of system at every stage

Transition To & From design and test environment continuously to identify and fix issues early- where changes are easier/less costly to make

>We showed an early prototype of a PA tuned to 5.8 GHz for WLAN applications from Agilent semiconductor group.

Simulation results showed a very nice agreement with the HW.

EVM was the metric we closely measured. This is a measurement that a PA designer does not necessarily care to know when doing the circuit design. Yet a necessary one dictated by IEEE802.11a.

Furthermore, the "signal source" and "signal analysis" via VSA were shared between simulation and test bench.

PA designer at this stage can concentrate on modification of circuit design- As we observed in this case in order to meet the power requirements- next step could be to use a parallel configuration of two PA to increase power level at 54 Mb/s to 17 dBm

| Test & Measurement Email Updates                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------|

| Keep up to date with Agilent's free Test and Measurement<br>Email Updates.                                                |

| As a subscriber, you will receive customized email updates that match your subject and frequency interests.               |

| Your updates will include support, products and services, applications, promotions, events and other areas.               |

| Subscribe today: <a href="http://www.agilent.com/find/emailupdates">www.agilent.com/find/emailupdates</a>                 |

| Our Privacy Statement at <u>http://www.agilent.com/go/privacy</u> describes our commitment to you regarding your privacy. |

| Please direct any questions about Agilent's privacy program to<br>privacy_advocate@agilent.com.                           |

| Page 36 Agilent Technologies                                                                                              |